## High-precision sensor front-end: Multi-path op-amp with chopping and nested miller compensation

Ali Taher Saber <sup>1,\*</sup> and Aland Faraidoon Ismael <sup>2</sup>

<sup>1</sup> Human Resources Section, College of Education for Humanities, University of Kirkuk, Kirkuk, Iraq.

<sup>2</sup> Independent Researcher in Electrical Engineering, Kirkuk, Iraq.

World Journal of Advanced Engineering Technology and Sciences, 2025, 16(03), 208–218

Publication history: Received on 02 August 2025; revised on 07 September 2025; accepted on 10 September 2025

Article DOI: <https://doi.org/10.30574/wjaets.2025.16.3.1337>

### Abstract

We introduce a low-noise, dual-path op-amp for precision sensing. Chopping lifts. During the chopping process, the circuit translates the low-frequency offset and flicker (1/f) noise components out of baseband and repositions them around the chopping sidebands commonly referred to as the chop band. A dedicated feedback path commonly called the ripple-reduction loop (RRL) detects the periodic ripple and drives a corrective signal that cancels it, thereby strongly attenuating the ripple component. To prevent an RRL-induced notch in the transfer, the signal is steered through two tracks: a low-frequency path (LFP) and a high-frequency path (HFP). The LFP pairs chopping with the RRL to keep the low band clean, while the HFP terminates in a class-AB output stage for improved energy efficiency under dynamic loading. A nested Miller compensation scheme (NMC) couples the two paths, yielding an approximately first-order closed-loop response over the intended bandwidth.

The prototype is implemented in 180 nm 1P6M CMOS, operates from 1800 mV, dissipates 174  $\mu$ W, and occupies 0.0118  $\text{cm}^2$  of active area. The measured UGBW is 3160 kHz.

**Keywords:** Amplifier; Nested Miller Compensation; Current-Feedback Instrumentation Amplifier; Input-Referred Noise

### 1. Introduction

The surge in Internet-of-Things (IoT) deployments has created demand for a wide range of sensors. In that landscape, MEMS devices are appealing for their small footprint, strong SNR, and favorable cost [1–3]. Because their output currents and voltages are tiny, the saturated iron-core superconducting fault current limiter (SISFCL) [4], significant amplification is necessary at the interface; as a result, the front-end op-amp must offer very large gain, present an exceptionally high input impedance to the source, and exhibit a low noise floor, thereby preserving signal fidelity and minimizing loading on the preceding stage, to ensure reliable readout [5–7].

Two well-established strategies are used to push the noise floor down: chopping and auto-zeroing [8]. Auto-zeroing operates in two steps: first, capturing offset and 1/f components on a capacitor, then subtracting them—so it is inherently discrete-time and introduces switching artifacts and folded high-frequency noise, which can be problematic for continuous-time operation. Chopped front ends, by contrast, are a better fit for continuous-time, low-power/low-noise front-end use cases [9].

Under chopping, the offset and 1/f terms are shifted by the chopper frequency ( $f_{\text{chop}}$ ), leaving mostly thermal noise in baseband but also creating ripple. By integrating the ripple observed at the output, the RRL drives input-side cancellation to suppress it [10]. The trade-off is that the RRL can introduce a notch around  $f_{\text{chop}}$ , trimming bandwidth.

\* Corresponding author: Ali T. Saber

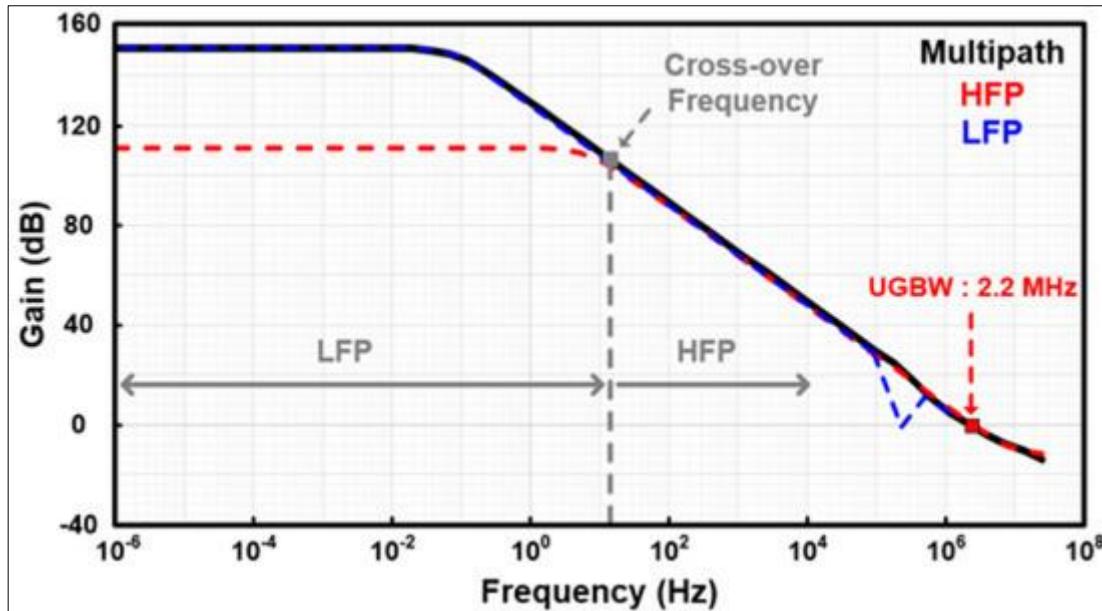

To avoid that penalty, the amplifier routes signals through dual channels—LFP handling low frequencies, HFP handling high. Nested Miller compensation (NMC) then blends their responses so the closed-loop behavior is effectively first-order across the band [11].

Over the specified bandwidth, the integrated loop is well modeled as first order. [11]. The HFP terminates in a class-AB output stage to keep power draw modest under dynamic loading.

**Silicon summary.** Built in 180 nm 1P6M CMOS, powered at 1800 mV, dissipating 174  $\mu$ W, with an active area of 0.0118  $\text{cm}^2$ . Measured UGBW = 3160 kHz and input-referred noise = 0.0118  $\mu$ V/ $\sqrt{\text{Hz}}$ , yielding NEF = 4.46.

## 2. Realization of the Dual-Path (LFP/HFP) Amplifier

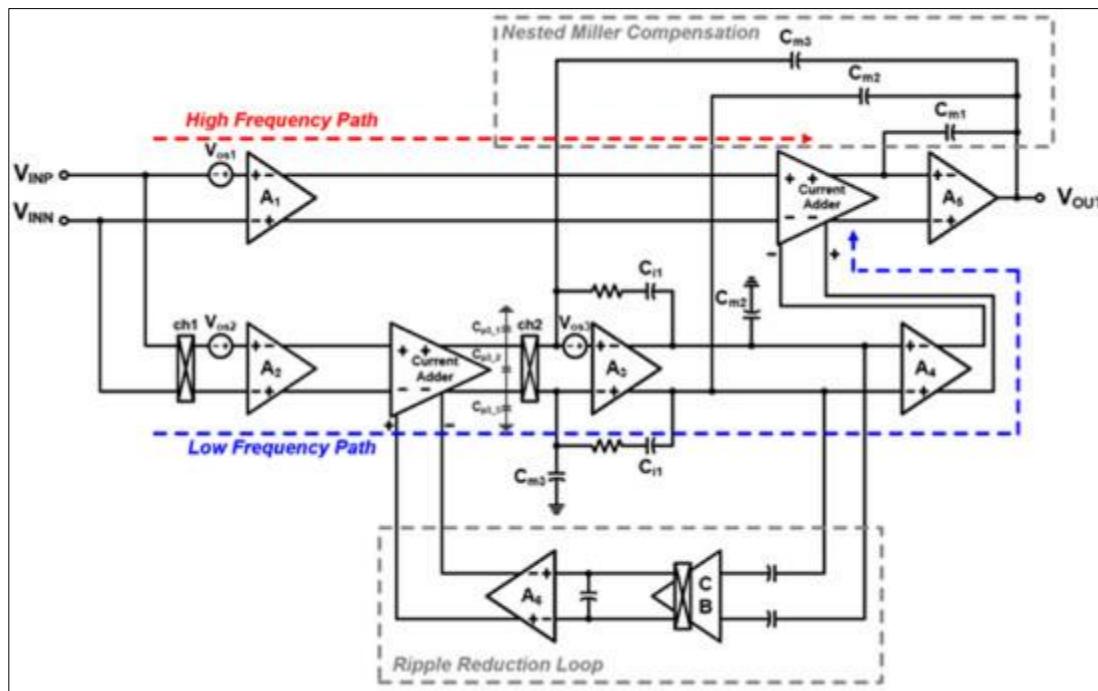

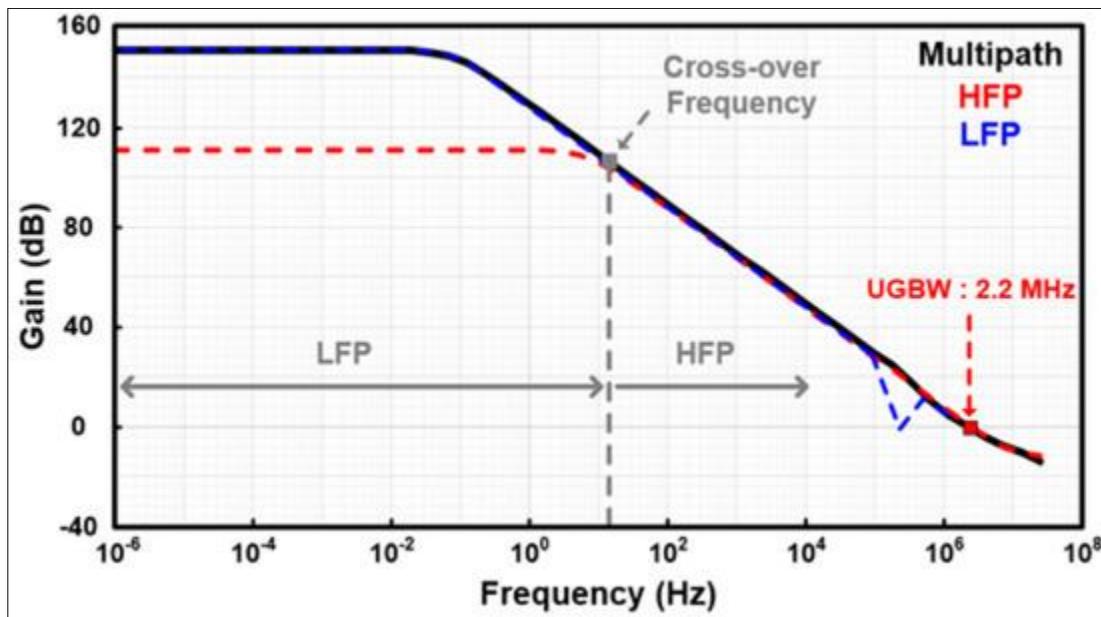

Figure 1 lays out a two-branch signal flow: a red-coded HFP and a blue-coded LFP. The LFP is deeper, using four gain stages; the HFP is lighter with two.

Inside the LFP, chopping knocks down offset and 1/f noise; the RRL completes the job by reducing the ripple. left by chopping. For additional cancellation, the current adder drives A6 against A2 with opposite polarity.

The branches are shaped to complement each other in frequency. The HFP behaves like an exhibit first-order dynamics set by  $Cm1$ ; the LFP shows second-order dynamics with poles at  $Cm1$  and  $Ci1$ . Nested Miller compensation (NMC) then blends the two responses into a stable overall loop.

**Figure 1** Proposed amplifier architecture featuring chopping and nested Miller compensation

## 2.1. LFP Structure and Noise Handling

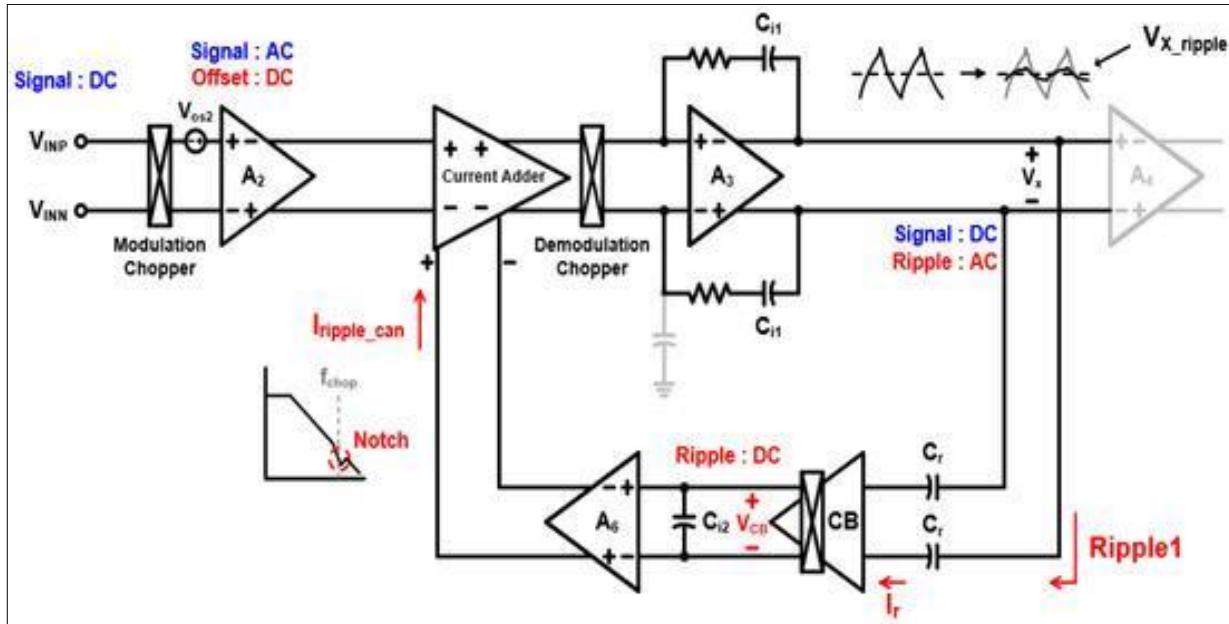

Figure 2 highlights LFP, built from four cascaded stages (vs. two in the HFP), largely governs offset and 1/f noise. Chopping translates the offset away from baseband and flicker components into the chopping band, reducing their footprint in the baseband.

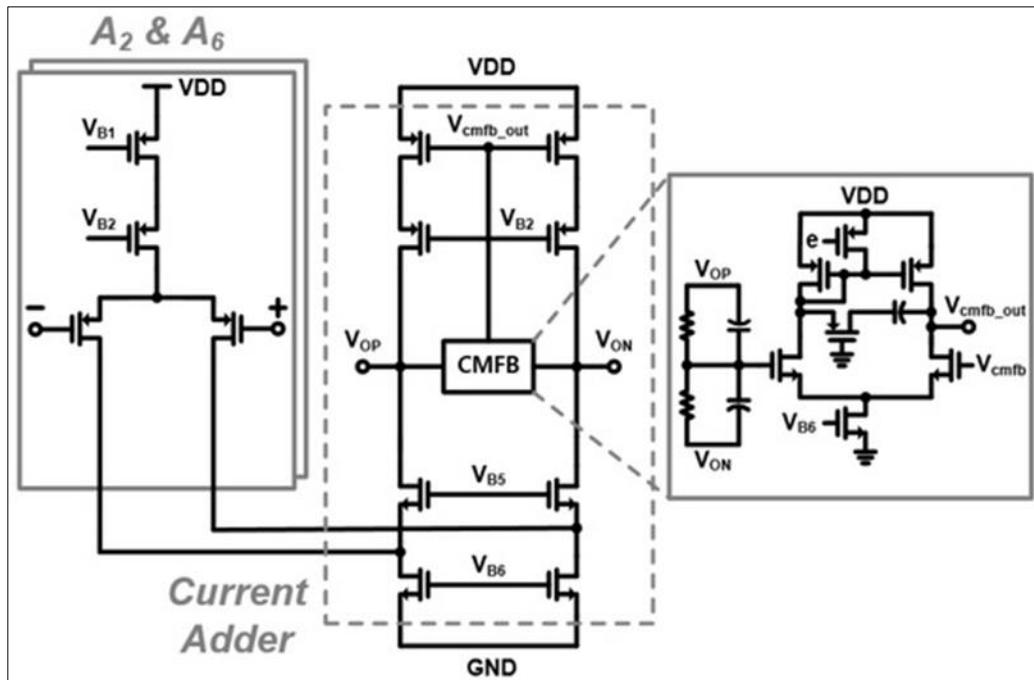

Figure 3 depicts the input section. The current-summing stage uses a common-mode feedback (CMFB) scheme realized as a closed loop around an auxiliary amplifier. Within this loop, the node labeled  $V_{cmfb}$  serves as the control point that governs the adder's output common-mode level and directs the loop's corrective action.

held at  $\frac{1}{2}$  VDD, which fixes the output common-mode levels  $V_{op}$  and  $V_{on}$  at  $\frac{1}{2}$  VDD.

Figure 2 LFP block diagram highlighting the ripple control loop (RRL)

Figure 3 Input front-end circuitry for the low-frequency path

## 2.2. Ripple Cancellation Loop: Concept and Implementation

$A_2$  turns the incoming voltage into a current, while  $A_6$  does the same for the ripple component. Those two currents hit the current adder with opposite polarity, so their difference knocks the ripple down. The adder's output current is integrated by  $A_3$ , creating the node voltage  $V_x$ . Then  $A_4$  converts  $V_x$  back to a current, which is summed with the High-Frequency Signal Path current at the adder ahead of  $A_5$ .

The demodulating chopper, working with the  $A_3$  integrator, acts on  $A_2$ 's offset and imprints a ripple at  $V_x$ . Here,  $Gm_2$  denotes the  $A_2$  transconductance parameter, and  $f_{chop}$  is the chopper frequency. The ripple at the  $A_3$  output is

$$V_{rip1} \approx (V_{os2} * Gm2) / (2 * Ci1 * fch).$$

If A4 has transconductance Gm4, further integration by A5 produces the output ripple

$$V_{rip2} \approx (V_{rip1} * Gm4) / (8 * Cm1 * fch).$$

To cut the ripple even more, the ripple-reduction loop is enabled. (RRL) is activated is engaged. The AC term Vrip1 passes through the coupling capacitor Cr, generating a current Ir given by

$$|Ir| \approx 2 * Cr * fch * |V_{rip1}|,$$

which then drives the current buffer (CB). Provided current sources M1, M2, M7, and M8 have high output impedance, the CB follows

$$V_{cb} = |Ir| * R_{cb} \text{ with } R_{cb} = Acb / (2 * Cr * fch),$$

Here, Acb denotes the DC gain produced by the NMOS cascode stage inside the CB block; in other words, it captures the steady-state amplification contributed by that cascode section. the CB. Routed through A6, this action yields an estimate of the cancellation current

$$I_{ripCan} \approx (Acb * Gm2 * Gm6 * V_{os2}) / (2 * Ci1 * fch).$$

With a 10 mV injected offset at Vx (Figure 5), the trace without RRL (red) shows about 68 mV of ripple, while enabling RRL (blue) reduces it to 8 mV, an  $\approx 88\%$  cut. The ripple-suppression factor is

$$F = I_{ripCan} / I_{os2} = (Acb * Gm6) / (2 * Ci1 * fch), \text{ with } I_{os2} = V_{os2} * Gm2.$$

**Figure 4** Bode magnitude/phase of the proposed design (simulation)

**Figure 5** Bode magnitude/phase of the proposed design (simulation)

### 2.3. Remaining Input Offset: Diagnosis and Design Fixes

In the LFP, chopping together with the RRL suppresses both offset and 1/f noise—if  $F$  is large, any remaining ripple fades to near zero. If  $F$  is large, any residual ripple is essentially negligible. By contrast, the HFP does not employ chopping, so its input offset is not canceled and shows up as the input's residual offset

The portion of residual input offset attributable to A1's offset ( $V_{os1}$ ) is defined by the expression in your derivation (kept unchanged per your rule).

The portion of residual input offset due to A1's offset  $V_{os1}$  is

$$V_{resOff1} \approx (A_h / A_l) * V_{os1},$$

where  $A_h$  and  $A_l$  are the HFP and LFP gains, respectively [14].

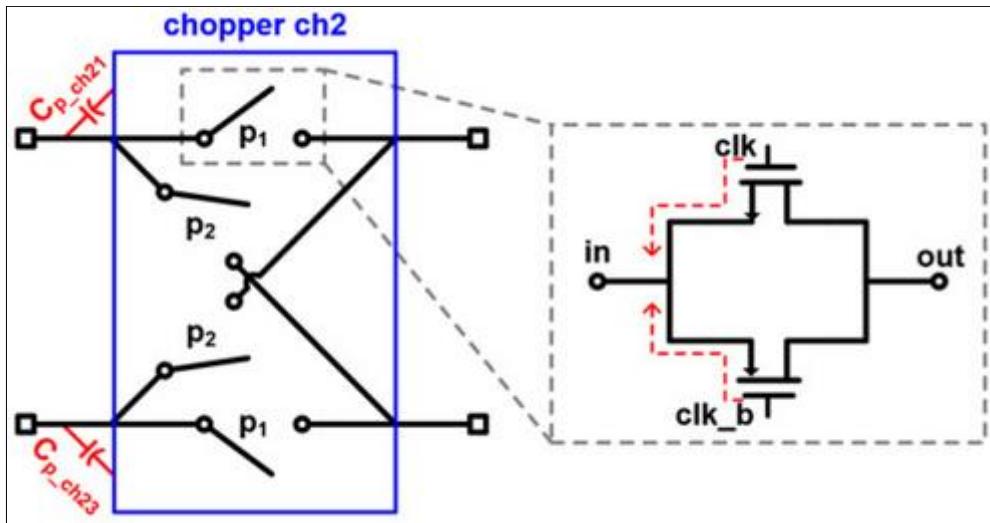

Another contribution comes from A3's offset  $V_{os3}$ . Chopper ch2 converts  $V_{os3}$  to a square wave and, through parasitics  $C_{p31}$ – $C_{p33}$ , drives an AC current set by A2's AC input [14]. Chopper ch1 then translates that AC term into a DC offset:

$$V_{resOff2} \approx 4 * V_{os3} * f_{ch} * C_{p3} / G_{m2},$$

with  $C_{p3} = C_{p31} + C_{p32} + C_{p33}$ .

Finally, ch2 uses four CMOS switches (Figure 8). Clock-feedthrough mismatch between  $C_{pch21}$  and  $C_{pch23}$  introduces an error that appears as an input offset [14]. The associated term is

$$V_{resOff3} \approx 2 * dC_{pch2} * V_{clk} * f_{ch} / G_{m2},$$

where  $dC_{pch2} = C_{pch21} - C_{pch2}$ .

**Figure 6** Schematic of one of the ch choppers

### 3. Bench Results and Metrics

#### 3.1. Core of Building the Chip and Experimental Setup

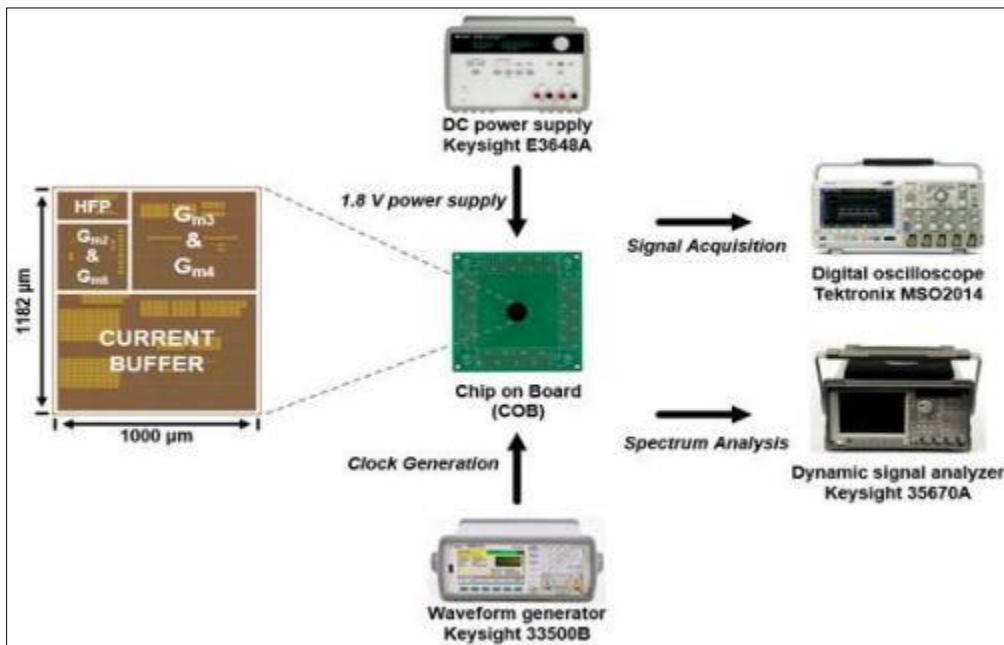

To validate the concept, we realized the multi-path operational amplifier as a silicon prototype manufactured in a conventional 180 nm CMOS technology node, enabling direct hardware evaluation of the design. 180 nm CMOS node. Figure 9 pairs a die shot with the bench hardware. Running from 1800 mV, the device dissipates 174  $\mu$ W and occupies 0.0118  $\text{cm}^2$  of active silicon.

For evaluation, the die was wire-bonded to a PCB. The clock and input were sourced from a waveform generator, the output traces were logged by a digital oscilloscope, and a dynamic signal analyzer handled the spectrum measurements to obtain spectral measurements.

**Figure 7** Chip micrograph and the laboratory test-and-measurement bench used to characterize and verify the proposed multi-path amplifier, including the instrumentation and fixtures used during evaluation

### 3.2. The Result of Bench and Metrics

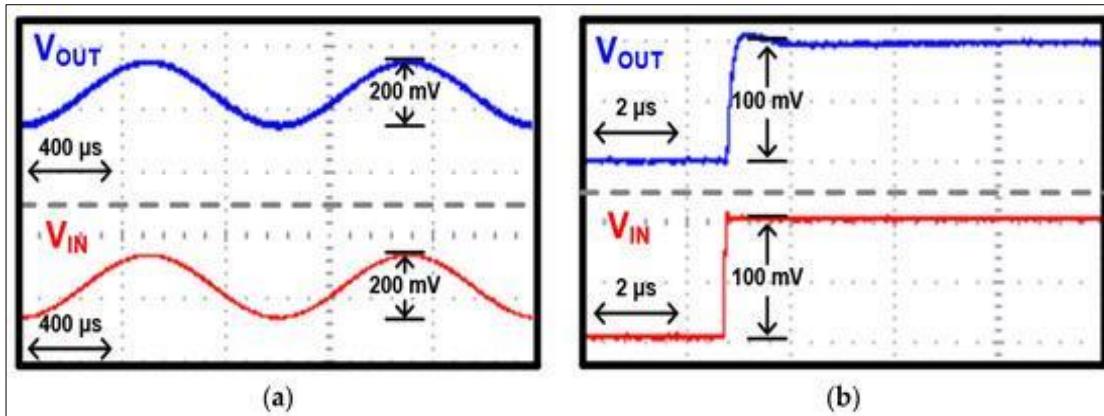

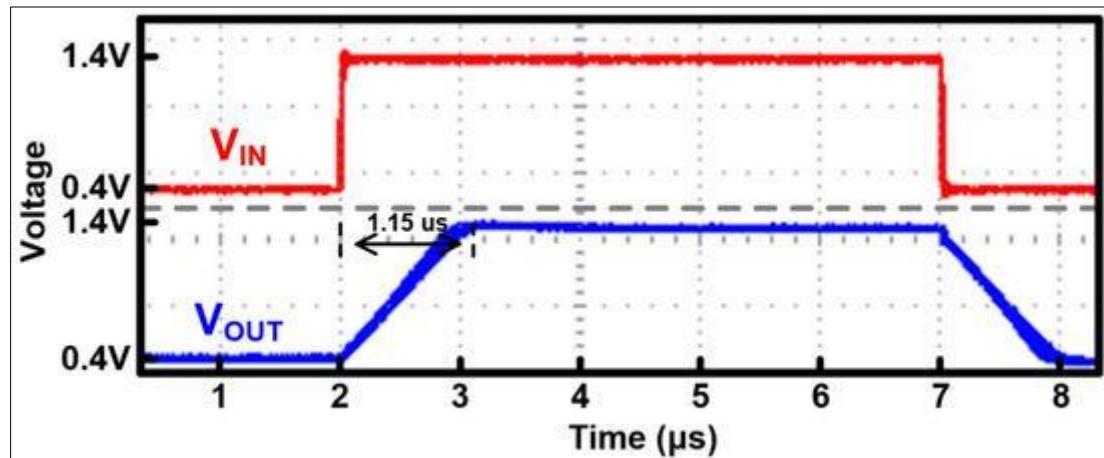

Using sinusoidal (a) and pulsed (b) stimuli, we evaluated the buffer behavior (Figure 10). For the sine case, the oscilloscope was set to 0.4 ms/div horizontally and 200 mV/div vertically. For the pulse case, the settings were 0.002 ms/div (timebase) and 50 mV/div (vertical). In both tests, the input (red) and output (blue) trace a 100 mV drive into a 0.05 nF load. The measured pulse rise time is 0.00115 ms.

**Figure 8** Buffer operation measurement results: (a) sine wave response, (b) pulse wave response

See Figure 11 for the slew check: the output (blue) tracks the input (red) step. The computed slew rate is

$$\text{Slew Rate} = dV_{\text{out}}/dt = 1000 \text{ mV} / 0.00115 \text{ ms} \approx 8.70 \times 10^5 \text{ mV/ms.}$$

**Figure 9** Slew rate measurement results

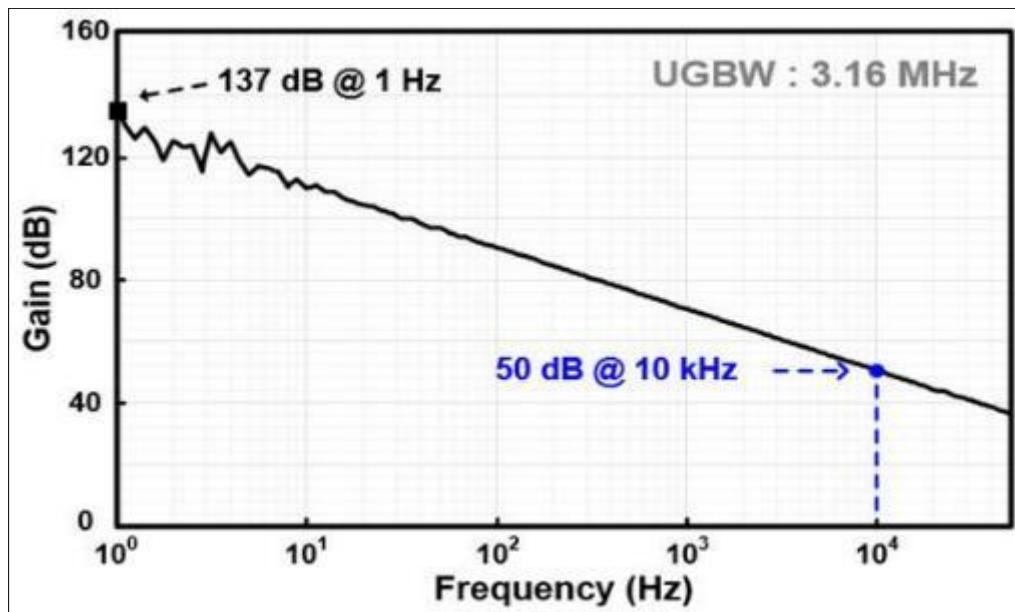

Figure 12 shows the open-loop sweep. The amplifier delivers a 135 dB DC gain, and the magnitude falls with a first-order slope coming in at 50 dB at 10 kHz and crossing unity at 3160 kHz (UGBW). The measured trace lines up well with the simulated curve in Figure 7.

**Figure 10** Open-loop gain measurement for the presented amplifier

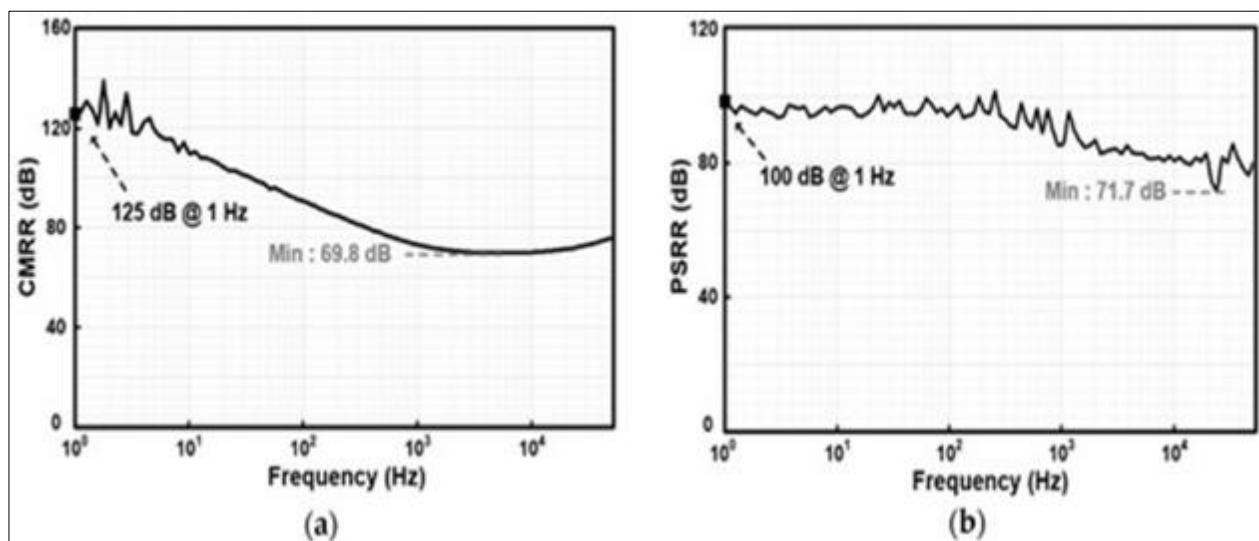

Figure 13 compiles the rejection data. At 0.001 kHz, the amplifier posts  $CMRR = 125$  dB and  $PSRR = 100$  dB. Over the sweep, the worst-case values are 69.8 dB for  $CMRR$  and 71.7 dB for  $PSRR$ .

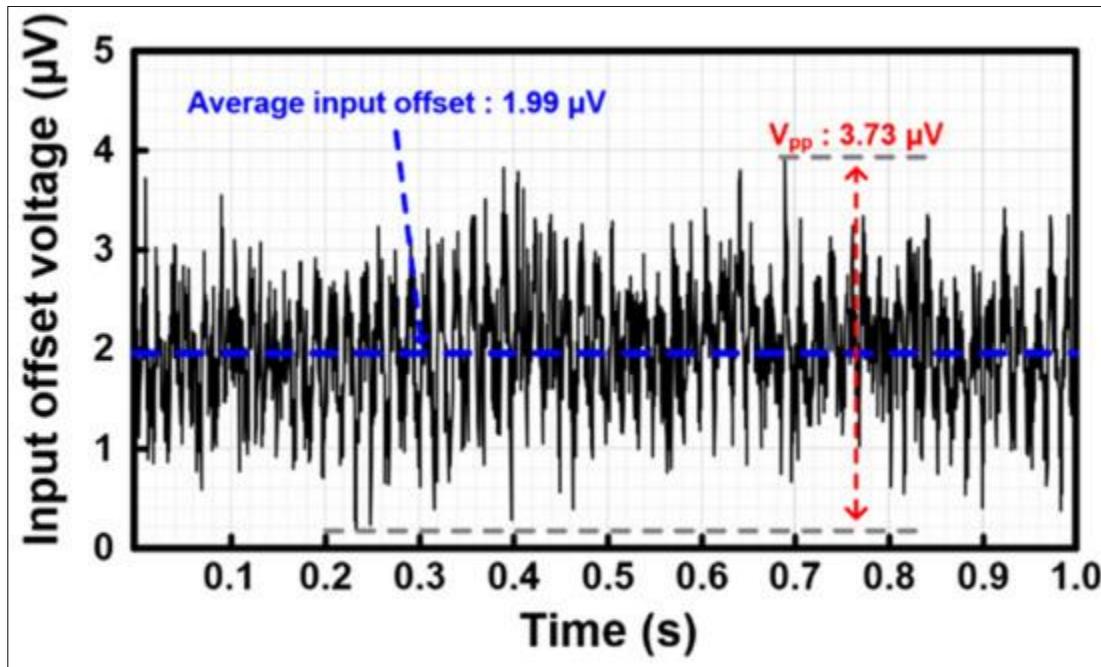

Figure 14. Input-referred offset across samples statistics across multiple samples: the average offset is 0.00199 mV, and the lowest value to the highest spread is 0.00373 mV.

**Figure 11** Measurement results for (a) CMRR and (b) PSRR

Figure 14 captures the input-referred offset results. Across the sample set, the mean offset is 0.00199 mV, and the peak-to-peak spread is 0.00373 mV.

**Figure 12** Statistical distribution of the input-referred offset

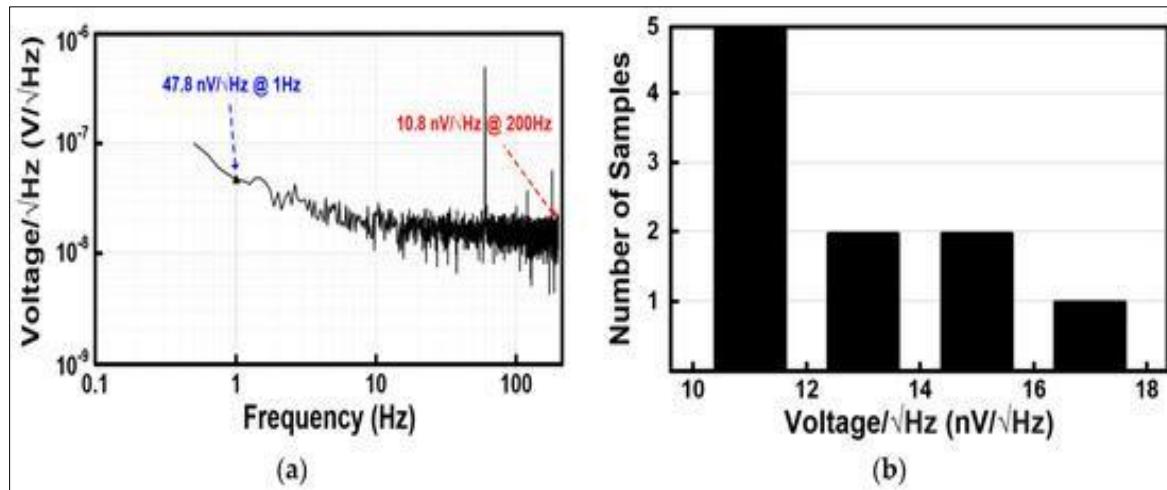

Noise was swept from 0.0005 kHz to 0.2 kHz (Figure 15). In Figure 15a, the input-referred noise density comes in at 0.0478  $\mu\text{V}/\sqrt{\text{Hz}}$  at 0.001 kHz and 0.0108  $\mu\text{V}/\sqrt{\text{Hz}}$  at 0.2 kHz. The histogram in Figure 15b—taken at 0.2 kHz across 10 samples—yields an average of 0.0118  $\mu\text{V}/\sqrt{\text{Hz}}$ .

**Figure 13** Noise measurement results: (a) input-referred noise density, (b) histogram of noise at 200 Hz

#### 4. Discussion

To stack this design against prior low-noise amps, we use the factor the noise efficiency (NEF) defined as  $\text{NEF} = V_{ni} * \text{sqrt}((2 * I_{tot}) / (\pi * U_T * 4 * k * T * \text{BW}))$  [15].

The prototype draws 0.0967 mA from 1800 mV, reaches UGBW = 3160 kHz, and posts input-referred noise = 0.0118  $\mu\text{V}/\sqrt{\text{Hz}}$ , which together yield NEF = 4.46. While the multi-path approach costs more area and power than some simpler options, it buys a stronger noise–bandwidth trade-off that drives this result.

## 5. Conclusion

We built a chopper-stabilized, two-path op-amp with nested Miller compensation for precision sensing. Chopping plus the RRL knocks down offset, 1/f noise, and ripple; the LFP/HFP split preserves bandwidth; and the compensation keeps the loop well behaved.

Made in 180 nm CMOS, the design uses  $0.0118 \text{ cm}^2$  of silicon and dissipates  $174 \mu\text{W}$ . It posts a slew rate of  $8.60 \times 10^5 \text{ mV/ms}$ , DC gain  $> 137 \text{ dB}$ , CMRR  $> 125 \text{ dB}$ , and PSRR  $> 100 \text{ dB}$ . With input-referred noise  $= 0.0118 \mu\text{V}/\sqrt{\text{Hz}}$  and UGBW  $= 3160 \text{ kHz}$ , the amplifier reaches NEF  $= 4.46$ , making it a strong fit for demanding precision-sensor interfaces.

## References

- [1] Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. *IEEE Sens. J.* 2010, 11, 925–933. [Google Scholar] [CrossRef]

- [2] Tan, Z.; Shalmany, S.H.; Meijer, G.C.; Pertijis, M.A. An energy-efficient 15-bit capacitive-sensor interface based on period modulation. *IEEE J. Solid State Circuits* 2012, 47, 1703–1711. [Google Scholar] [CrossRef]

- [3] Ladani, L.; Nelson, S. A novel piezo-actuator-sensor micromachine for mechanical characterization of micro-specimens. *Micromachines* 2010, 1, 129–152. [Google Scholar] [CrossRef]

- [4] Ali Taher Saber and Aland Faraidoon Ismael, “Coordinated overcurrent protection in distribution grids incorporating an active superconducting fault current limiter,” *Global Journal of Engineering and Technology Advances*, vol. 24, no. 2, pp. 175–180, 2025, doi: 10.30574/gjeta.2025.24.2.0244. [Google Scholar]

- [5] Belloni, M.; Bonizzoni, E.; Fornasari, A.; Maloberti, F. A micropower chopper—CDS operational amplifier. *IEEE J. Solid State Circuits* 2010, 45, 2521–2529. [Google Scholar] [CrossRef]

- [6] Kim, H.; Song, H.; Park, Y.; Ko, H. Low noise resistive analog front-end with automatic offset calibration loop. In Proceedings of the 2015 International SoC Design Conference (ISOCC), Gyungju, Korea, 2–5 November 2015. [Google Scholar]

- [7] Wu, R.; Huijsing, J.H.; Makinwa, K.A. A  $21\text{b} \pm 40 \text{ mV}$  range read-out IC for bridge transducers. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011. [Google Scholar]

- [8] Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. *Proc. IEEE* 1996, 84, 1584–1614. [Google Scholar] [CrossRef] [Green Version]

- [9] Ko, Y.; Kim, H.; Park, Y.; Mun, Y.; Cho, D.I.D.; Ko, H. Low-Noise Chopper-Stabilized Resistive Readout Integrated Circuit with Ripple Rejection Loop. *Sens. Mater.* 2017, 29, 927–933. [Google Scholar]

- [10] Wu, R.; Makinwa, K.A.; Huijsing, J.H. A chopper current-feedback instrumentation amplifier with a  $1 \text{ mHz}$   $1/\text{f}$  noise corner and an AC-coupled ripple reduction loop. *IEEE J. Solid State Circuits* 2009, 44, 3232–3243. [Google Scholar] [CrossRef] [Green Version]

- [11] Eschauzier, R.G.; Kerklaan, L.P.; Huijsing, J.H. A 100-MHz 100-dB operational amplifier with multipath nested Miller compensation structure. *IEEE J. Solid-State Circuits* 1992, 27, 1709–1717. [Google Scholar] [CrossRef] [Green Version]

- [12] Monticelli, D.M. A Quad CMOS Single-Supply Op Amp with Rail-to-Rail Output Swing. *IEEE J. Solid-State Circuits* 1986, 21, 1026–1034. [Google Scholar] [CrossRef] [Green Version]

- [13] Eschauzier, R.G.; Hogervorst, R.; Huijsing, J.H. A programmable 1.5 V CMOS class-AB operational amplifier with hybrid nested Miller compensation for 120 dB gain and 6 MHz UGF. *IEEE J. Solid State Circuits* 1994, 29, 1497–1504. [Google Scholar] [CrossRef]

- [14] Witte, F.; Huijsing, J.H.; Makinwa, K.A. Dynamic Offset Compensated CMOS Amplifiers; Springer: Berlin, Germany, 2010; pp. 23–40. [Google Scholar]

- [15] Steyaert, M.S.J.; Sansen, W.M.C. A Micropower Low-Noise Monolithic Instrumentation 284 Amplifier for Medical Purposes. *IEEE J. Solid-State Circuits* 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- [16] Fan, Q.; Huijsing, J.H.; Makinwa, K.A. A  $21 \text{ nV}/\sqrt{\text{Hz}}$  Chopper-Stabilized Multi-Path Current-Feedback Instrumentation Amplifier with  $2 \mu\text{V}$  Offset. *IEEE J. Solid State Circuits* 2011, 47, 464–475. [Google Scholar]

- [17] Burt, R.; Zhang, J. A micropower chopper-stabilized operational amplifier using a SC notch filter with synchronous integration inside the continuous time signal path. In Proceedings of the 2006 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006. [Google Scholar]

- [18] Kusuda, Y. A  $5.9 \text{ nV}/\sqrt{\text{Hz}}$  chopper operational amplifier with  $0.78 \mu\text{V}$  maximum offset and  $28.3 \text{ nV}/^\circ\text{C}$  offset drift. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011. [Google Scholar]

- [19] Ong, G.T.; Chan, P.K. A power-aware chopper-stabilized instrumentation amplifier for resistive wheatstone bridge sensors. *IEEE Trans. Instrum. Meas.* 2014, **63**, 2253–2263. [Google Scholar] [CrossRef]

- [20] Lue, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. *IEEE J. Solid State Circuits* 2019, **54**, 2255–2265. [Google Scholar] [CrossRef]

- [21] Butti, F.; Piotto, M.; Bruschi, P. A Chopper Instrumentation Amplifier with Input Resistance Boosting by Means of Synchronous Dynamic Element Matching. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2017, **64**, 753–794. [Google Scholar] [CrossRef]